Part Number: TM4C1294KCPDT

お世話になります。

標記のTM4C1294KCPDTI3を使用した製品の設計中ですが、ハードリセットに付き確認したいです。

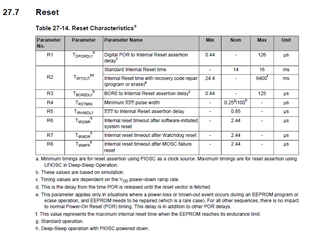

・#69(RST)端子によるリセットではなく、パワーオンリセットは可能でしょうか?タイミング等、どこかに記載がありますでしょうか?

・#69(RST)端子を利用したハードリセットの仕様に付き、確認したいのですが、パルス幅の規定等、どこかに記載がありますでしょうか?

お忙しいところ恐縮ですが、ご回答のほどお願い致します。

以上です。