Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

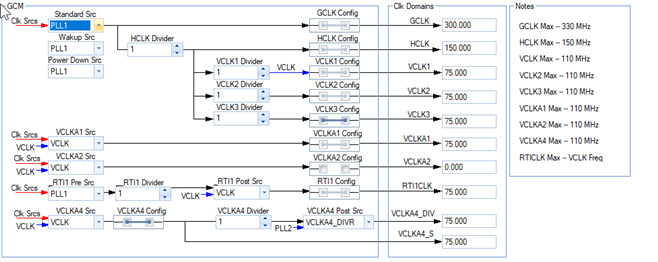

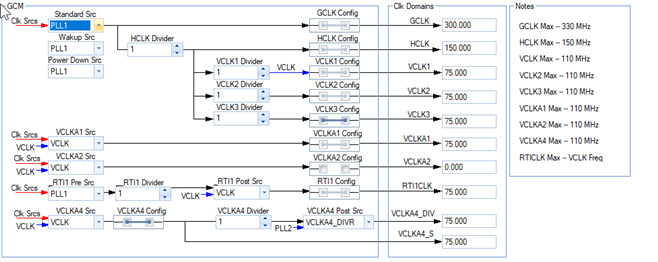

当我使用HALCoGen 去配置TMS570 的CLK时,发现我只能配置VCLK3 是否导通。

能否为我解释一下CLK Demains 当中各个CLK的含义,以及在当前配置下的状态(是否使用,是否在代码当中配置好了)?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

当我使用HALCoGen 去配置TMS570 的CLK时,发现我只能配置VCLK3 是否导通。

能否为我解释一下CLK Demains 当中各个CLK的含义,以及在当前配置下的状态(是否使用,是否在代码当中配置好了)?

Hi HL,

You should be able to change the VCLK3 divider on the GUI. The VCLK3 is a clock divided down from HCLK, ad it can be HCLK/1,/2,.../16.

The VCLK3 is the clock source for EMIF, ECAPx, ePWMx, Ethernet and eQEP modules.

Which version of HALCoGen are you using? The latest one is 4.07.01.

GCLK: R5F CPU clock frequency

HCLK: system clock frequency

VCLK: primary peripheral clock frequency

VCLK2: Secondary peripheral clock frequency

VCLK3: Secondary peripheral clock frequency

VCLKA1 - Primary asynchronous peripheral clock frequency

VCLKA2 - Secondary asynchronous peripheral clock frequency

VCLKA4 - Secondary asynchronous peripheral clock frequency

You can use the default settings. The default value for VCLK3 is HCLK/(1+1) = 150/2=75MHz which is a valid range (<110MHz).