Hi experts,

My understanding of the ESM - nERROR dependency was that the nERROR-Pin is always in LOW state, when there is an error bit set in one of the ESM registers. Which would mean that the nERROR pin can not be reset while the Error in the ESM is not cleared.

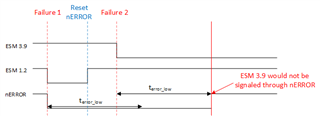

But when looking at the documentation again, Figure 16-7 in the Techhnical reference Manual suggests otherwise:

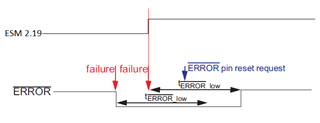

For clarification I added the state of the ESM 2.19 bit to Figure 16-7.

(Q1) Is it possible to reset the nERROR Pin although an error like ESM 2.19 is still present und not cleared?

Thank you and best regards,

Max