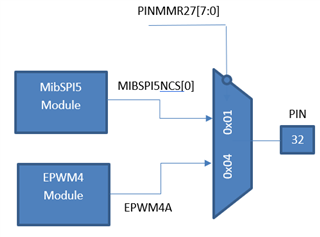

Hi, I don't understand how I can write code that will read the state of the MIBSPI5NCS[0] signal connected to pin 32 of the tms570. I understand how this signal is similar to N2HET2[12], for example and I know that N2HET1[12], when configured as an output, can be toggled using:

gioToggleBit(hetPORT1, 12);

In deed, the previous level of support had ref'ed a similar question in which it was suggested that the following could be used:

gioSetBit(mibspiPORT5, bit_index, value)

However, although I guess I could replace "gioSetBit" with "gioGetBit" (something I've already considered) but confusion remains re MIBSPI5NCS[0]:

- The first thing that confuses me is that the address used in the def of mibspiPORT5 is the same as that for spiPORT5:

#define mibspiPORT5 ((gioPORT_t *)0xFFF7FC18U

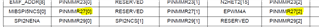

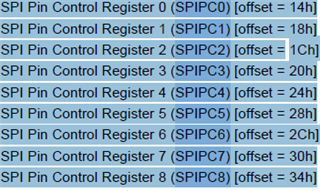

#define spiPORT5 ((gioPORT_t *)0xFFF7FC18U) - The 0xFFF7FC18 address points to SPIPC1 reg (offset 18h) and then the gioGetBit() fn's use of "port->DIN" gets us to SPIPC2 (offset 1Ch = 18h+4) but I don't understand what value to use for "port" in the call to gioGetBit().

- How do I ensure that MIBSPI5NCS[0] is configured as an input?

- Table 4-21 in the SPNU515C doc is the only place in this doc that ref's MIBSPI5NCS[0] but this table confuses the hell out me.