Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

Hi,

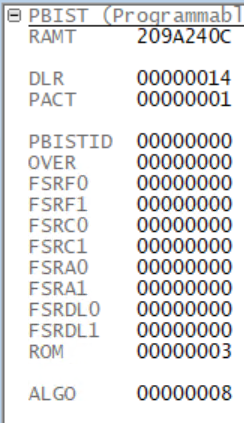

- When the internal RAM memory test is performed using the March13N algorithm for Single-port considering the Groups 29 and 30 for L2RAMW, I am encountering L2RAMW - double-bit ECC uncorrectable error (Group 3 Channel 3 error) [sometimes, bus error also] which affects the further execution of application leading to an exception.

Referring to the C:\ti\Hercules\SafeTI Diagnostic Library\2.4.0\demo_app\common\source\app_main_NoOS.c, came accross the below statement:

"/* nERROR with PBIST_RAMGROUP_29_L2RAMW (PBIST_RAMGROUP_30_L2RAMW)

* Running PBIST on Cache memories need special considerations to be taken care

* of in application. */"

Please confirm if the PBIST memory test can be performed on the internal RAM test. (If it cannot be performed, please also clarify the reason)

What is the alternative to test the Internal RAM test and how can it be integrated into the PBIST sequence?

Also, what are the special considerations to be taken care of when PBIST is run on Cache memories? Please clarify.

- This is regarding the PBIST tests: Referring to the demo code in C:\ti\Hercules\SafeTI Diagnostic Library\2.4.0\demo_app\HALCoGen\TMS570LC4357_NoOS\source, the sequence of built-in self-tests is not provided in the startup code. Request you to provide the exact sequence of built-in self-test to be followed.

Thanks

Tirumala.