Other Parts Discussed in Thread: HALCOGEN, TMS570LS1224, TMS570LS3137

Could you please explain the functionality of eFuse module. The TRM didn't provide much information about efuse module.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Could you please explain the functionality of eFuse module. The TRM didn't provide much information about efuse module.

Hi Subash,

There is an array of eFuses that are used to configure various electrical parameters that affect the Flash banks, Flash pump and the multiple SRAM instances on-chip. This array of eFuses is programmed during factory-test of the part, and is scanned on power-up as part of the device start-up sequence (not software-controlled). This process is termed the "eFuse auto-load" and there is SECDED logic implemented to correct any single-bit error and detect double-bit error during this auto-load. Any error during this auto-load process is flagged in the appropriate ESM status register.

The efcCheck() routine generated by HALCoGen is used to ensure correct operation of this SECDED logic. This is critical in ensuring that the eFuse auto-load was completed correctly and that the SECDED logic used to correct any single-bit errors is also operating correctly.

Hi QJ, if I may stick my nose into this issue, I have a couple of comments as this is an area I have been investigating myself in order to achieve the required SIL for my project:

Marcus

1. This function should be called by _c_int00() if "Enable EFUSE Self Test" is checked in HALCoGen "SAFETY INIT" window. This is a HAL SW bug. The efcCheck() and checkefcSelfTest() need to be added to _c_int00() manually.

2. checkefcSelfTest() needs to be called separately.

Just had a "nasty thought": in your reply to Subash, you stated that:

array of eFuses is programmed during factory-test of the part, and is scanned on power-up as part of the device start-up sequence

Does the TMS570 do this scanning if the power remains on BUT nPORRST is asserted (e.g. the TPS65381 watchdog reports an error)?

Marcus

Hi Marcus,

Yes. Whenever the nPORRST is asserted, the eFuse values are read and loaded into the internal registers.

Hi QJ/Marcus,

Thank you so much for your inputs. Upon power-up when we check for ESM register (ESMSR4 ESM Status Register 4 - FFFF F558h) it is showing error despite the eFuse status register (EFCERRSTAT - FFF8 C000 ) is zero. As per TRU ESM status register set with respect to eFuse status. could you please tell me why this conflict?

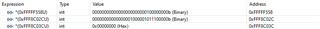

I have attached snapshot of these register values.

Hi Subash,

The ESM 1:40 and ESM 1:41 can also be set by the stuck-at-zero test. The stuck-at-zero test is used to test the connections between the eFuse controller and the ESM module. After the stuck-at-zero test, the ESM error should be cleared.

Did you perform the stuck-at-zero test? or did you program the EFC EFCBOUND register at 0xFFF8C01C?

Hi QJ,

We are performing the stuck at zero test and it is passed successfully, subsequently we are performing the following steps as per TRM:

• Write 0x00000258 to the self test cycles register (EFCSTCY) at address 0xFFF8C048.

• Write 0x5362F97F to the self test signature register (EFCSTSIG) at address 0xFFF8C04C.

• Write 0x0000200F to the boundary register at address 0xFFF8C01C.

we are polling bit 15 of 0xFFF8C02C and once done we are seeing ESM 1:40 is being set, but eFuse status register (EFCERRSTAT - FFF8 C000 ) is zero. Could you please tell us the root cause of this issue?

Thanks,

Subash

we are polling bit 15 of 0xFFF8C02C and once done we are seeing ESM 1:40 is being set, but eFuse status register (EFCERRSTAT - FFF8 C000 ) is zero. Could you please tell us the root cause of this issue?

The stuck at zero test doesn't set any bit of EFC status register. The corresponding bit of EPC pin register is set.

Hi QJ,

As per the 4th point mentioned in Section 32.3.2.5 of TRM, neither of ESM group 1 channels 40 and 41 should be set, after the ECC Logic Self Test is completed.

As per Table 6-35 in the TMS570LS3137 Datasheet, ESM group 1 channel 40 is set when any bit in the EFC Error Status Register (EFCERRSTAT) is set.

I have attached register values snapshot for your reference!

Thanks,

Subash

Hi Subash,

Both are correct. But the description in 32.3.2.5 is not clear.

If self-test failed, the ESM 1.41 will be set.

The 32.3.2.5 wants to say that if the test passes, the ESM 1.41 is not set.