Part Number: TMS570LC4357

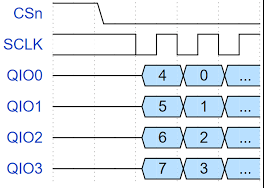

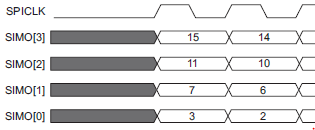

Is it possible to use a Quad SPI device connected to MIBSPI5.

I see they talk about parallel mode 2-2, 4-4, 8-8....

I have a a S70FL01GS (dual 512Mbit) spi memory which I can run as 2 independent dies, or I can run it in quad mode...

just not sure if the "parallel mode" descirbed in the HERC ref manual (section 28.2.6.6.5...SPNU563A–March 2018)

appreciate the response as usual

thank you!