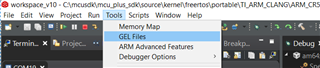

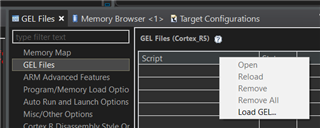

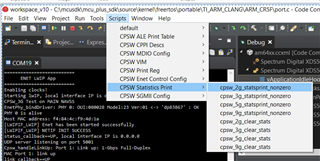

The CPSW IP in MCU+ devices supports debug/diagnostics stats. How do I print those stats using gel files provided in the MCU+ SDK Enet LLD?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.