Part Number: TM4C123AH6PM

Hello all,

We have one application that uses a TM4C123AH6PM. One of the GPIO's is connected to the gate of a N-ch mosfet which controls a power line.

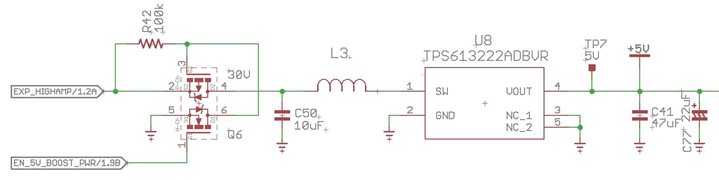

The EN_5V_BOOST_PWR is connected directly to GPIO PB3, pin #48 of the IC. There is no other connection on this signal - one end in the MCU, the other in the gate.

The pad is configured as output, 4mA, standard.

Over the past months we've had several failures on this GPIO. When that happens, the voltage out of the MCU no longer goes above ~1.2V. It goes to zero if the pin is set low, but when set high it won't reach the expected 3V3.

Schematic is shown above. The issue has happened in several different boards, different MCU batches, but the symptom is always the same. And the only solution is to replace the MCU.

It does seem to be a hardware issue with a lot of possible guesses, but such a simple design leaves us little inspiration to look for reasons - so we are reaching out here for ideas of where to look.

Regards

Bruno