Other Parts Discussed in Thread: HALCOGEN,

Hi TI-experts,

We are using TMS570LC43xx Microcontroller.

Requirement is to reset the board in some specific error condtion.

Please suggest Halcogen-API to generate soft reset.

Thanks and Regards,

Anil

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI-experts,

We are using TMS570LC43xx Microcontroller.

Requirement is to reset the board in some specific error condtion.

Please suggest Halcogen-API to generate soft reset.

Thanks and Regards,

Anil

TMS570LC4357: Is there sample code for reboot or reset has some suggested code to generate a software reset, albeit I haven't tested the suggested code.

Hi Anil,

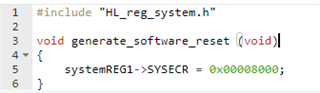

Please use systemREG1->SYSECR = 0x00008000; to generate SW reset.

The HalCoGen doesn't generate SW reset API. You can use the function from Chester:

SYSECR register should be written in privileged mode.

There is no software API or function to perform the hard reset (cold reset).

Thank you for reply. As there in no TI or halcogen software API to hard reset the board TMS570LC4357, can we use internal watchdog to hard reset the controller? Also, please suggest alternate easy ways to hard reset and details of the same. It will be really helpful.

The watchdog can generate either a warm reset or a NMI to the CPU. But It can not generate a cold reset.

Can you please clarify that "hard reset" is nPORRST?

can we get a sample code for user mode to privilege mode switching and vice versa?

Sorry I don't have example code available.

Cold reset: Occurs on device power up (POR), or pulling down the nPORRST pin. Upon cold reset, everything in the device is being reset.

Warm reset: Warm reset types are not necessarily applied globally within device. We can use a warm reset to reset a subset of the device logic. Warm reset events include software reset, watchdog time-out, nRST, CPU reset after LBIST, etc.

Memory is usually not reset and maintains the previous state. The only exception is that we cannot guarantee the state of the memory when a nPORRST happens. Since this reset is asynchronous, it could happen while a write operation to a RAM takes place and could disrupt this operation. We can't guarantee what will happen if this write is not finished correctly. All other resets are synchronous and there is not problem with the RAM content.