Part Number: TMS570LC4357

Hi Team,

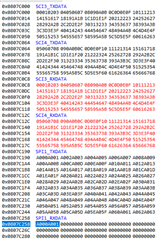

In Our Application based on the TMS570LC4357 processor, we are having the following DMA channels used for the below-mentioned purpose:

SPI1 Rx - DMA Channel 9 - Operated in Slave Mode with Baudrate 10MHz - High Priority channel

SCI3 Rx - DMA Channel 5 - Baudrate 57600 - Low Priority

SCI3 Tx - DMA Channel 4 - Baudrate 57600 - Low Priority

SCI4 Rx - DMA Channel 7 - Baudrate 9600 - Low Priority

SCI4 Tx - DMA Channel 6 - Baudrate 9600 - Low Priority

Here, SPI1 Rx is configured as the highest priority due to its criticality in nature, where we receive the data continuously on this Peripheral. Additionally, in the system, we have configured the Low Priority channels in the Round Robin scheme and High Priority channels in the Fixed scheme as mentioned in the reference manual. However, in the application currently, we are missing one/2 bytes sporadically for the SCI3 Reception i.e. for the DMA Channel 5. We have tried changing the priorities of these DMA Channels but were not been able to get any breakthrough for the same. As there is Only One DMA Engine on this processor, we were suspecting the DMA is getting hogged and sometimes not getting a chance to Receive the data for SCI3. Thus, for further analysis, we wanted to calculate the throughput of the DMA engine by using all these DMA channels with the mentioned data rate. We would like to know is there any method that can help us in calculating the DMA throughput for our application here to resolve this issue?

Regards,

Shivam