Other Parts Discussed in Thread: HALCOGEN

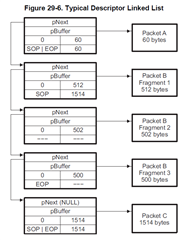

We are using EMAC peripheral in our project for external communication, if the packet size is more than 1500 then we fragment it. As per TRM (29.2.6.5.7 ) the End of Pocket is set by EMAC when the complete packet is received.

The question is when the external system sends 2K bytes, it will fragment the EMAC packet as two frames of 1500 bytes and 500 bytes. How does the EMAC peripheral set the EOP flag in Rx descriptor after receiving all the fragments.

Thanks,

Subash