Hi Experts

Regarding UART (Rx) and GPIO is set Input,

How much the rise time and fall time are allowed for UART (Rx) and GPIO (Input) ?

I couldn't find the upper limit as the rise and fall time on the datasheet.

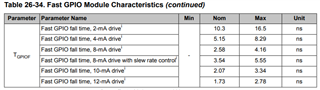

The following characteristics on the datasheet (Rev B, page 1592 - 1593).

the characteristics is set GPIO as output, right?