Other Parts Discussed in Thread: HALCOGEN

Dear all,

My board has an FPGA connected to EMIF_nCS2 (async device 1, mapped at 0x60000000 memory address) of the TMS570LS3137 EMIF interface.

I set up the peripheral via HalCoGen with 8 bit data bus, select strobe mode, and extended wait.

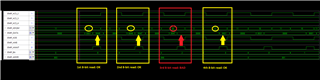

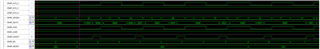

When I read 8 bit variables starting from address 0x60000000 I can see that the first 2 reads have correct EMIF_ADDR, correct EMIF_BA[1:0], correct EMIF_nCS2 and correct EMIF_nDQM[1:0] signals.

The third read, the one with EMIF_BA[1:0] = 0b10 has bad EMIF_nDQM signals: both bits to 0.

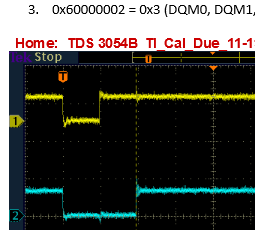

This condition is not vaild, thus the FPGA publics 0x00 on the data bus. The picture below shows the signals on the data bus

This issue appears every time the EMIF_BA[1:0] equals 0b10.

I read that the mpu should set that address segment as DEVICE type on some forums but this doesn't seem to resolve the problem.

Any advice for configuring the EMIF peripheral?

Thanks in advance,

Federico Gobetti.