Part Number: TMS570LS3137-EP

Other Parts Discussed in Thread: HALCOGEN

Hello,

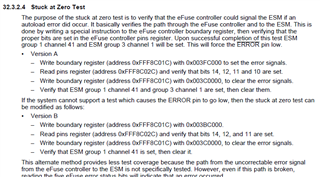

In the eFuse module, before starting the stuck-at-zero test, the following bits are already being shown as set(1) in the EFC Boundary Control Register:

- EFC Self Test Error

- EFC Single Bit Error

- EFC Instruction Error

- EFC Autoload Error

Because of this, the stuck-at-zero test is failing. What could be the reason for all these bits to be set at once? And is there any way to reset these bits?