Other Parts Discussed in Thread: HALCOGEN

Hey,

We are starting to use TMS570LS1114ZWT, in the past we worked with TMS570LS0914PGE.

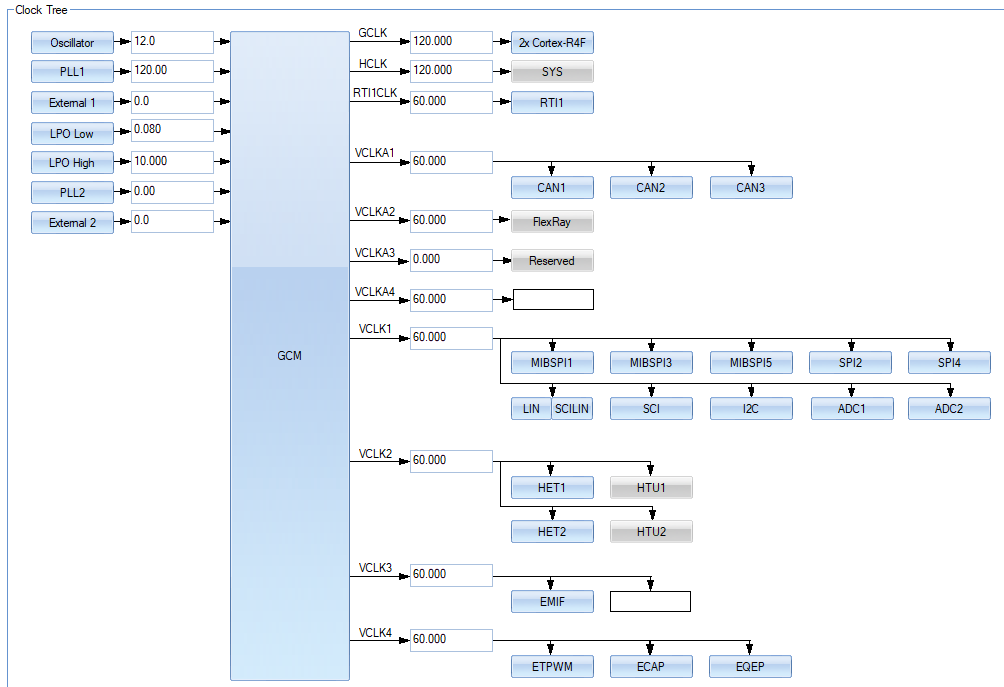

Our Oscillator has 12MHz. We verified that with an oscilloscope.

With Halcogen we generated a initial Project. We tried to set the core Frequency to 120Mhz(and also 160MHz and 180MHz). However, we are using this 120MHz in our old project. Our configurations are below.

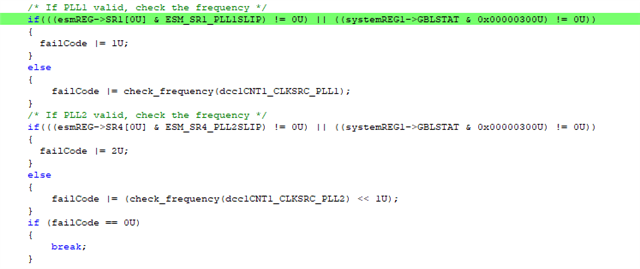

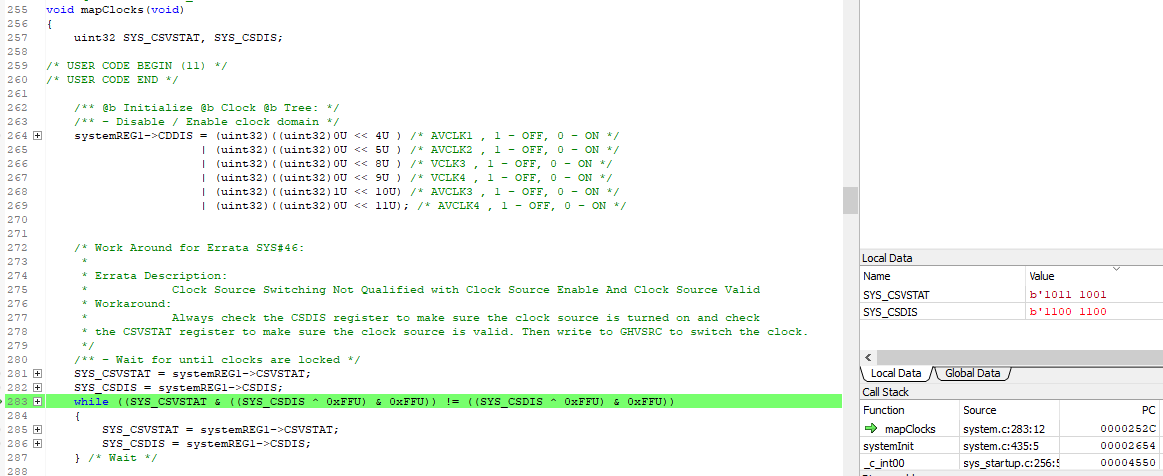

When we run our genereated code. It stack at the point when the programm waits until the clocks are locked.

Do you have an idea how we can check that the hardware is designed correctly? are there some points which should be measured?

Or how can we verify that there are no missing configuration settings in halcogen?

Here are my configurations:

Best regards,

Thorben