Other Parts Discussed in Thread: HALCOGEN

Hello there,

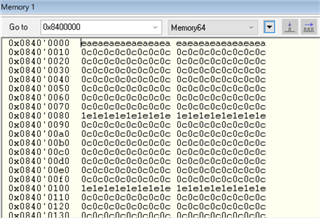

In our project the ECC is enabled to detect SRAM double-bit error. We're looking for a way to simulate double-bit parity error and to see its effect.

However upon reading SPNU499c paragraph 6.6 Emulation / Debug Mode Behavior of the TCRAM module, it looks like it is not possible to force this error with the Debugger in Debug Mode.

What are the techniques to make sure that the SRAM ECC was correctly enabled and it effect is confirmed (like asserting nERROR pin) when error is detected, must like in the case of the SECDEC Flash Error Detection and Correction Control Register 1, by reading a predefined address located at the OTP?

Many thanks!