Hi All,

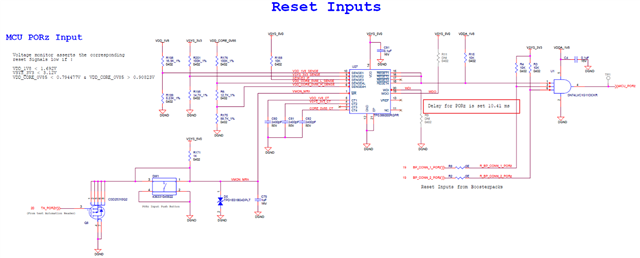

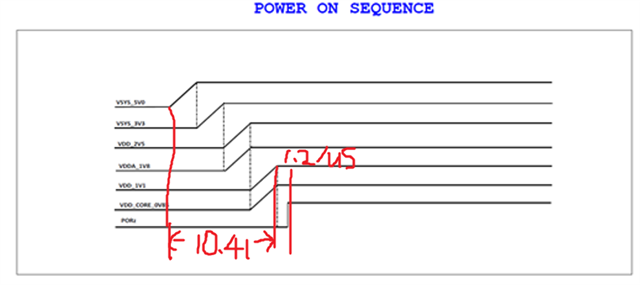

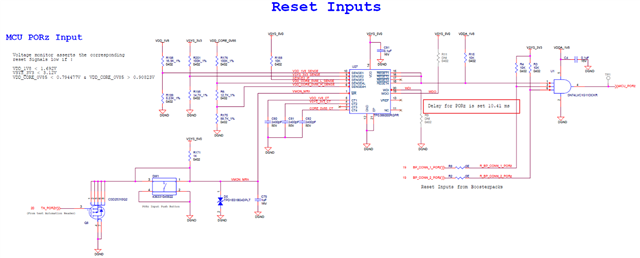

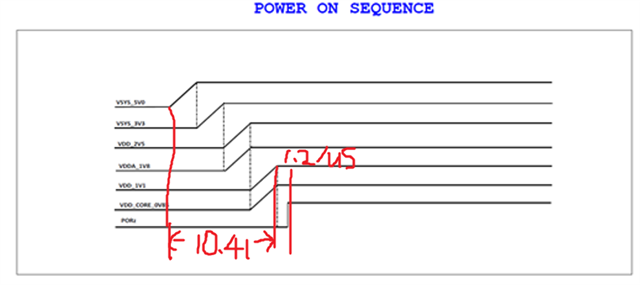

1.I want to know what's mean about the Delay for PORz is set 10.41 ms, Power-on sequence is right?

2. MCU_PORz is a key input from the outside, how long is its effective low level?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi All,

1.I want to know what's mean about the Delay for PORz is set 10.41 ms, Power-on sequence is right?

2. MCU_PORz is a key input from the outside, how long is its effective low level?

Hi Shaoxing,

1. The statement "Delay for PORz is set 10.41ms" refers to the delay that is programmed into the TPS386000RGPR with the capacitors on CT1, CT2, and CT4. The delay between the inputs on SENSE1, SENSE2, or SENSE4 crossing the threshold and the corresponding nRESET1, nRESET2, or nRESET4 output changing is set to 10.41ms.

2. I am not sure what exactly you are asking. The parameter RST27 in the table you show indicates that the PORz_OUT and MCU_PORz have a minimum pulse low time of 1200ns. If you need more information than this, please let us know what you are looking for exactly and we can try to better help.

Thanks,

Mike

Hi Shaoxing,

The image you show from the LP-AM243 schematic shows the sequencing of the rails as implemented on the LaunchPad. The PORz in the image refers to the MCU_PORz signal on the LaunchPad schematic. However, the delays you have labeled are incorrect per the implementation of the TPS386000RGPR reset controller. Since the reset outputs for SENSE1 (1.8V), SENSE2 (3.3V), and SENSE4 (0.85V) are all tied together, and they all have the same programmed delay of 10.41ms, the PORz is delayed by 10.41ms from the last voltage to cross the threshold. Based on the timing diagram shown, the last voltage to cross the threshold is the 0.85V Core Voltage rail, so the PORz is delayed by 10.41ms from when 0.85V becomes valid.

Thanks,

Mike

Yes, on the LP-AM243, the RST1 timing is set to 10.41ms through the TPS386000RGPR.