Part Number: RM46L852

Other Parts Discussed in Thread: HALCOGEN

Hello,

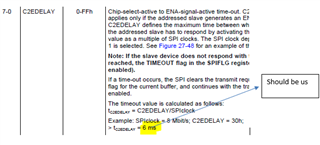

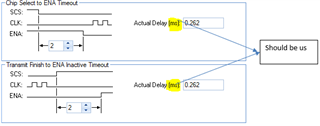

Just double checking that my reverse engineering is correct concerning C2EDELAY and T2EDELAY fields of SPIDELAY register, can you confirm my findings? I refer to RM46 TRM: SPNU514C – March 2018 but same looks to be also in RM44 SPNU608A – March 2018.

1) chapter 25.9.19 (SPIDELAY) says that C2EDELAY is ms and T2EDELAY is us. My experiment is that C2EDELAY is also us?

2) HALCoGen (04.07.01) shows in SPIx Delays tab that both would be ms but should be us?

3) TRM nor HALCoGen does not say anything about value 0 in such registers but looks like given delay formula (delay=regval*spiclk) applies only while regval != 0 thus value 0 is kind of disable of the feature?

Just a side note but basically looks like you cannot these delays with MCU-MCU communication with 10M clk the maximum wait time is 25,5us and 20M clk only 12,5us, practically impossible to time own DMA sending in master side to match other MCU readiness so that it would respond anything feasible in that time frame...