Dear TI,

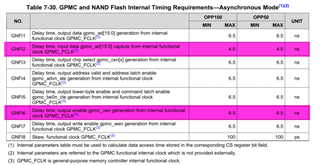

I am using GPMC in 16 bit, non multiplex, NOR asynchronous mode. GPMC CONFIG5.RDACCESSTIME specifies the read sampling point. I cannot find corresponding setup & hold time spec in SPRSP65B data sheet. F12 & F13 rows of Table 7-50 on page 220 contain such spec for NOR sync mode only.

What about my case?

Regards, Kalman