Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

Hi,

I would like to store reset information in SRAM, and read it after a warm reset performed. I've tried every option, but after any kind of reset when the PC set to the reset entry vector all RAM data initialized back to 0.

I've put my variable in noinit section and used the linker script below:

#define NON_VOLATILE_DATA __attribute__ ((section(".noinit")))

NON_VOLATILE_DATA static char data[16];

#define SRAM_SIZE 0x00080000

#define STACKS_START_ADDR 0x08000000

#define STACKS_SIZE 0x00004e00

#define KRAM_START_ADDR (STACKS_START_ADDR + STACKS_SIZE)

#define KRAM_SIZE 0x00000800

#define RAM_START_ADDR (KRAM_START_ADDR + KRAM_SIZE)

#define RAM_SIZE (SRAM_SIZE - NOINIT_RAM_SIZE - KRAM_SIZE - STACKS_SIZE)

#define NOINIT_RAM_START_ADDR (RAM_START_ADDR + RAM_SIZE)

#define NOINIT_RAM_SIZE 0x000000100

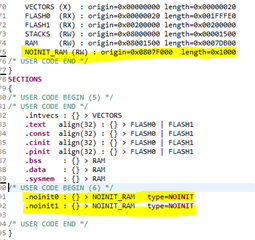

MEMORY

{

VECTORS (X) : origin = 0x00000000 length = 0x00000020

KERNEL (RX) : origin = 0x00000020 length = 0x00008000

FLASH0 (RX) : origin = 0x00008020 length = 0x001F7FE0

FLASH1 (RX) : origin = 0x00200000 length = 0x00200000

STACKS (RW) : origin = STACKS_START_ADDR length = STACKS_SIZE

KRAM (RW) : origin = KRAM_START_ADDR length = KRAM_SIZE

RAM (RW) : origin = RAM_START_ADDR length = RAM_SIZE

NOINIT_RAM (RW) : origin = NOINIT_RAM_START_ADDR length = NOINIT_RAM_SIZE

}

SECTIONS

{

.intvecs : {} > VECTORS

/* FreeRTOS Kernel in protected region of Flash */

.kernelTEXT align(32) : {} > KERNEL

.cinit align(32) : {} > KERNEL

.pinit align(32) : {} > KERNEL

/* Rest of code to user mode flash region */

.text align(32) : {} > FLASH0 | FLASH1

.const align(32) : {} > FLASH0 | FLASH1

/* FreeRTOS Kernel data in protected region of RAM */

.kernelBSS : {} > KRAM

.kernelHEAP : {} > RAM

.bss : {} > RAM

.data : {} > RAM

.sysmem : {} > RAM

.noinit : {} > NOINIT_RAM type=NOINIT

}

I have even tried to disable initialization of the memory block before the reset:

l2ramwREG->MEMINITDOMAIN = 0x7f;

But non of the above was working, the RAM always read 0 after the reset.

Is there any possible way to store data in SRAM without it initializing on reset?

Thank you!