Other Parts Discussed in Thread: HALCOGEN

Model initialization code:

_enable_interrupt_();

/* Setup ADCs */

adcStartConversion(adcREG1, adcGROUP1);

adcStartConversion(adcREG2, adcGROUP1);

kickerReg->KICKER0 = 0x83E70B13U;

kickerReg->KICKER1 = 0x95A4F1E0U;

pinMuxReg->PINMMR35 = 0x0000;

kickerReg->KICKER0 = 0x00000000U;

kickerReg->KICKER1 = 0x00000000U;

/* setup etPWM */

etpwmSetCount(etpwmREG1, 1000);

etpwmSetCount(etpwmREG2,500);

etpwmSetCount(etpwmREG3, 300);

etpwmSetCounterMode(etpwmREG1, CounterMode_UpDown);

etpwmSetCounterMode(etpwmREG2, CounterMode_UpDown);

etpwmSetCounterMode(etpwmREG3, CounterMode_UpDown);

etpwmSetSyncOut(etpwmREG1,SyncOut_CtrEqZero);

etpwmSetSyncOut(etpwmREG2,SyncOut_EPWMxSYNCI);

etpwmSetSyncOut(etpwmREG3,SyncOut_EPWMxSYNCI);

etpwmREG2->TBCTL |= (uint16)2U << 1U; // PHSEN

etpwmREG3->TBCTL |= (uint16)2U << 1U;

/* Configure mthe module to set PWMA value as 1 when CTR=0 and as 0 when CTR=CmpA */

etpwmActionQualConfig_t configPWM;

configPWM.CtrEqPeriod_Action = ActionQual_Disabled;

configPWM.CtrEqZero_Action = ActionQual_Disabled;

configPWM.CtrEqCmpAUp_Action = ActionQual_Set;

configPWM.CtrEqCmpADown_Action = ActionQual_Clear;

configPWM.CtrEqCmpBUp_Action = ActionQual_Disabled;

configPWM.CtrEqCmpBDown_Action = ActionQual_Disabled;

etpwmSetActionQualPwmA(etpwmREG1, configPWM);

etpwmSetActionQualPwmA(etpwmREG2, configPWM);

etpwmSetActionQualPwmA(etpwmREG3, configPWM);

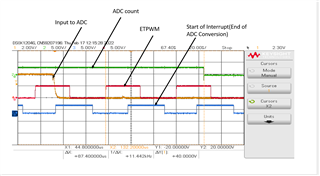

/* Enable trigger for SOC */

etpwmEnableSOCA(etpwmREG1, CTR_ZERO, EventPeriod_FirstEvent);

etpwmClearEventFlag(etpwmREG1, Event_SOCA);

etpwmTriggerEvent(etpwmREG1,Event_SOCA);

etpwmDisableCounterLoadOnSync(etpwmREG1);

etpwmEnableCounterLoadOnSync(etpwmREG2, 0, 0x2000);

etpwmEnableCounterLoadOnSync(etpwmREG3, 0, 0x2000);

etpwmEnableTimebasePeriodShadowMode(etpwmREG1);

etpwmEnableTimebasePeriodShadowMode(etpwmREG2);

etpwmEnableTimebasePeriodShadowMode(etpwmREG3);

etpwmEnableCmpAShadowMode(etpwmREG1, LoadMode_CtrEqZero);

etpwmEnableCmpAShadowMode(etpwmREG2, LoadMode_CtrEqZero);

etpwmEnableCmpAShadowMode(etpwmREG3, LoadMode_CtrEqZero);

etpwmDeadBandConfig_t deadbandconfig;

deadbandconfig.halfCycleEnable = true;

deadbandconfig.inputmode = PWMA_RED_FED;

deadbandconfig.outputmode = PWMB_FED_PWMA_RED;

deadbandconfig.polarity = Invert_PWMB;

etpwmSetDeadBandDelay(etpwmREG1,112,112);

etpwmSetDeadBandDelay(etpwmREG2,112,112);

etpwmSetDeadBandDelay(etpwmREG3,112,112);

etpwmEnableDeadBand(etpwmREG1, deadbandconfig);

etpwmEnableDeadBand(etpwmREG2, deadbandconfig);

etpwmEnableDeadBand(etpwmREG3, deadbandconfig);

ADC Read from RAM:

#define adc1Group1_ReadFirst (*(volatile uint32 *)0xFF3E0000U)

#define adc1Group1_ReadSecond (*(volatile uint32 *)0xFF3E0004U)

#define adc1Group2_ReadFirst (*(volatile uint32 *)0xFF3A0000U)

#define adc1Group2_ReadSecond (*(volatile uint32 *)0xFF3A0004U)

#define adc1Group1FLAG (*(volatile uint32 *)0xFFF7C038U)

#define adc2Group1FLAG (*(volatile uint32 *)0xFFF7C238U)

#define adc1Group1RAMReset (*(volatile uint32 *)0xFFF7C014U)

#define adc2Group1RAMReset (*(volatile uint32 *)0xFFF7C214U)

PhaseA

if (%<u1_val>==1){

%<y1_val>= adc1Group1_ReadFirst & 0xFFFU;

}

else if (%<u1_val>==0)

{

%<y1_val>= adc1Group1_ReadSecond & 0xFFFU;

}

else

{

%<y1_val>=255;

}

adc1Group1RAMReset|=0x00000010U;

adc1Group1FLAG|=0x09U;

PhaseB

if (%<u1_val>==1){

%<y1_val>= adc1Group2_ReadFirst & 0xFFFU;

}

else if (%<u1_val>==0)

{

%<y1_val>= adc1Group2_ReadSecond & 0xFFFU;

}

else

{

%<y1_val>=255;

}

Attached .dil for Halcogen Config: