Part Number: TMS570LS1114

Other Parts Discussed in Thread: HALCOGEN,

Dear TI experts,

we are trying to interface an ISSI IS42S16100H-7TLI on a custom board via the EMIF module.

We are operating the CPU with PLL1 with 180 Mhz and the EMIF with 90 Mhz. During consecutive write operations to the SDRAM we notice that only every second to third cell is written correctly. When we lower the CPU frequency to 90 Mhz such that f_cpu = f_emif = 90 Mhz, consecutive writes to SDRAM work almost 100 %. Read operations seem to work independent of frequency settings.

Test code:

__attribute__((section(".farbss"))) volatile uint16_t sdram_far[100] = { 0 }; // test array in sdram

/**

* main.c

*/

int main(void)

{

uint16_t sdram_read[100] = { 0 };

// write to sdram far memory

for(uint16_t i = 0; i < 100; i++)

{

sdram_far[i] = i;

}

// reading from sdram

for(uint16_t i = 0; i < 100; i++)

{

sdram_read[i] = sdram_far[i];

}

}

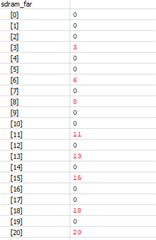

case 1: f_cpu = 180 Mhz, f_emif = 90 Mhz case 2: f_cpu = f_emif = 90 Mhz (only write of cell 3 is omitted)

Timing settings in Halcogen:

Our suspicion is, that we are overreaching the emifs bandwidth in case 1. So how should consecutive memory accesses to sdram be done from software side, when f_cpu > f_emif? Is there an application note for TMS570LS1114 we could follow?

Help is highly appreciated as we are working on a large client project.

Kind regards

David