Part Number: TMS570LC4357

We are failing to shut down the DCAN peripheral as described in TRM:

27.11.1 Entering Global Power Down Mode.

The DCAN waits until a bus idle state is recognized. Then it will automatically set the Initbit to indicate that the global power down mode has been entered.

At the time of shutting down the bus is not idle - some other devices are driving the CAN bus. Our DCAN just finished some self test and it has been reset to init state.

But we really need to disable this device independently to fact, that CAN bus isn't in idle state.

The problem persists even when entered and confirmed a Local Power Down Mode:

27.12.1 Entering Local Power Down Mode,

With setting the PDA bits, the DCAN module indicates that the local power down mode has been entered.

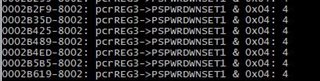

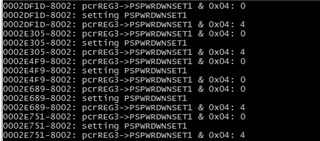

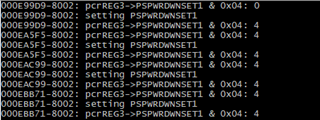

The DCAN is still regularly failing to enter the Global Power Down Mode as long as the CAN bus is not idle (i.e. setting of the corresponding PSPWRDWNSET bit fails).

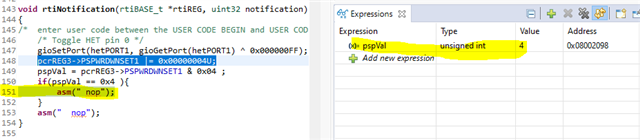

We happened to come across a workaround that solves our problem but it is some undocumented behavior.

If we set just the SWR bit in DCAN CTL register, without setting the init bit, then we can reliably enter the Global Power Down Mode even when the CAN bus is not idle.

This behavior could possibly be explained as a forced reset state the DCAN is being held in (as the init bit has not provided a way out).

However, we would like to know how to properly enter the Global Power Down Mode when there is traffic on the bus, or if our workaround is legit.