Part Number: TMS570LC4357

Hi Team,

In Our Application based on the TMS570LC4357 processor, we are having the following DMA channels used for the below-mentioned purpose. Given Table also defines the data rate currently used by the application for establishing the required communication:

|

Peripheral |

DMA Channel No |

Data Rate |

Configured Priorities |

Functionality in Application |

|

SPI1 Rx |

9 |

Slave Mode with 10MHZ baud rate (32 bit for every 125 ms) |

High |

Marker Beacon |

|

SCI3 Rx |

5 |

57600 (330-340 bytes for every 100ms) |

Low |

TE2 tool |

|

SCI3 Tx |

4 |

57600 (301 bytes for every 100ms) |

Low |

TE2 tool |

|

SCI4 Rx |

7 |

115200 (data size considering the max throughput with the Baud Rate) |

Low |

GNSS |

|

SCI4 Tx |

6 |

115200 (data size considering the max throughput with the Baud Rate) |

Low |

GNSS |

Here, SPI1 Rx is configured as the highest priority due to its criticality in nature, where we receive the data continuously on this Peripheral.

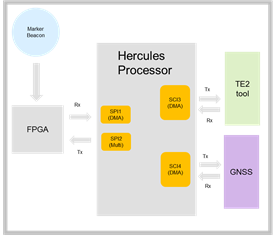

The Below diagram gives the overview about the Peripheral Interface with the Hercules Processor.

Here, Currently in our application, we are facing issues while receiving the data over SCI3, as mentioned in the earlier tickets provided below the ticket links:

As per the reference manual, we tried to configure the round robin scheme for the low priority channels and Fixed scheme for high priority channels. However, the missing of one/2 bytes sporadically for the SCI3 Reception i.e. for the DMA Channel 5 is still there. We had tried changing the priorities of these DMA Channels but it did not help in resolving.

Furthermore as a workaround we have observed that, when the SCI3 tx is switched into the polling mode instead of DMA, that time we are not seeing any kind of issues for SCI3 reception, which indicates that DMA engine of the processor, is not able to handle this all DMA channels in the system.

We would like to understand why the DMA is not allowing to process all these channels. and wanted to understand what would be the approach to use the DMA in better way such that all these DMA channels will get served properly.

I also have attached the method, which we are using to configure the DMA packets for SCI3.UartDma.xlsx

Request team to help us in providing the correct approach to use all these required peripherals Using DMA.

Regards,

Shivam