Part Number: TMS570LC4357

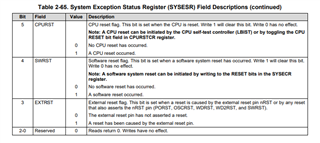

The datasheet for the TMS570LC43x states that the EXTRST (external reset flag) will be set during a SWRST event. However, when triggering a SWRST event, only the SWRST flag is set and not the EXTRST flag.

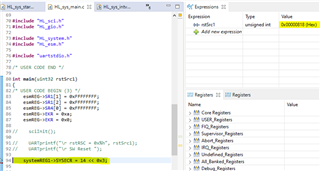

Here is the function call for initiating the SWRST:

void warmReset(void)

{

systemREG1->SYSECR |= SYS_RESET_BIT;

return;

}

During the reset, the _c_int00() function is called to initialize the processor. During this phase, the getResetSource() function is called which checks the state of the SYSESR register. This register shows the flag set during the reset event. Before this function is called, the SYSESR register is reading 0x00000010 (only the SWRST bit is set), when I would have expected it to be 0x00000018 (SWRST bit and the EXTRST bit).

Without the EXTRST flag getting set, the startup code is never able to return that a SW_RESET event has occurred, which causes future issues.

/* SourceId : SYSTEM_SourceId_008 */

/* DesignId : SYSTEM_DesignId_008 */

/* Requirements : HL_CONQ_SYSTEM_SR9 */

resetSource_t getResetSource(void)

{

register resetSource_t rst_source;

if ((SYS_EXCEPTION & (uint32)POWERON_RESET) != 0U)

{

/* power-on reset condition */

rst_source = POWERON_RESET;

/* Clear all exception status Flag and proceed since it's power up */

SYS_EXCEPTION = 0x0000FFFFU;

}

else if ((SYS_EXCEPTION & (uint32)EXT_RESET) != 0U)

{

SYS_EXCEPTION = (uint32)EXT_RESET;

/*** Check for other causes of EXT_RESET that would take precedence **/

if ((SYS_EXCEPTION & (uint32)OSC_FAILURE_RESET) != 0U)

{

/* Reset caused due to oscillator failure. Add user code here to handle oscillator failure */

rst_source = OSC_FAILURE_RESET;

SYS_EXCEPTION = (uint32)OSC_FAILURE_RESET;

}

else if ((SYS_EXCEPTION & (uint32)WATCHDOG_RESET) !=0U)

{

/* Reset caused due watchdog violation */

rst_source = WATCHDOG_RESET;

SYS_EXCEPTION = (uint32)WATCHDOG_RESET;

}

else if ((SYS_EXCEPTION & (uint32)WATCHDOG2_RESET) !=0U)

{

/* Reset caused due watchdog violation */

rst_source = WATCHDOG2_RESET;

SYS_EXCEPTION = (uint32)WATCHDOG2_RESET;

}

else if ((SYS_EXCEPTION & (uint32)SW_RESET) != 0U)

{

/* Reset caused due to software reset. */

rst_source = SW_RESET;

SYS_EXCEPTION = (uint32)SW_RESET;

}

else

{

/* Reset caused due to External reset. */

rst_source = EXT_RESET;

}

}

else if ((SYS_EXCEPTION & (uint32)DEBUG_RESET) !=0U)

{

/* Reset caused due Debug reset request */

rst_source = DEBUG_RESET;

SYS_EXCEPTION = (uint32)DEBUG_RESET;

}

else if ((SYS_EXCEPTION & (uint32)CPU0_RESET) !=0U)

{

/* Reset caused due to CPU0 reset. CPU reset can be caused by CPU self-test completion, or by toggling the "CPU RESET" bit of the CPU Reset Control Register. */

rst_source = CPU0_RESET;

SYS_EXCEPTION = (uint32)CPU0_RESET;

}

else

{

/* No_reset occured. */

rst_source = NO_RESET;

}

return rst_source;

}

Additionally, to confirm that the EXTRST flag is functioning correctly, when I perform an actual external warm reset, by driving the nRST pin low, the result is the SYSESR register being 0x00000008 as expected.

I am currently working off of the TMS570LC43x Hercules Development Kit and have used the WARM_RSTn button to test the above.

To summarize, should the SWRST flag automatically also flag the EXTRST flag?

Relative page of TRM is page 199