Hi Team,

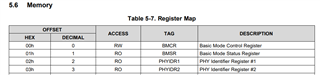

For our application on TMS570LC4357 controller, we are using the MDIO interface to communicate with the DP83848 PHY chip, where we are able to establish the communication successfully and getting the ping responses, the way we desired. However, as per our requirement we want to configure and read back the destination mac address for which we have to access the ReceivePerfectMatchDataRegister#3 (RXFPMD3) register whose address is 0x40A4. Here to communicate with the PHY we are sending the PHY register address to the MDIO interface. But, as per the reference manual of controller, the maximum bits we can use for the PHY register address is 5 (REGADR field of USERACCESS0 register), So we are finding challenges to communicate with the PHY for configuring/reading the RXFPMD3 register values.

In this scenario, we are looking for a way to configure such registers of PHY using MDIO? Isn't it possible for us to configure such registers using MDIO? Request team to help us in resolving this issue.

Regards,

Shivam