Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

The ARM technical manual for R5 MCUs says that the divide-by-zero exception mask can be disabled by writing to the DZC bit in the Secondary Auxiliary Control Register. [ 4-26].

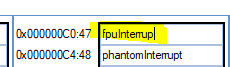

How do I check that the exception/interrupt is being called? I am using halcogen with version 9.3.0 of CCS.

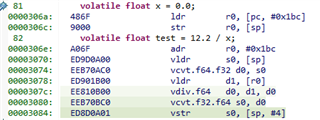

I have verified that the DZC is set to 1 and that the compiler isn't optimizing the divide by zero away. Here is the code that I am using to the test the feature and a screenshot of the assembly stepping.

volatile float x = 0.0;

volatile float test = 12.2 / x;