Other Parts Discussed in Thread: SYSCONFIG

Hi,

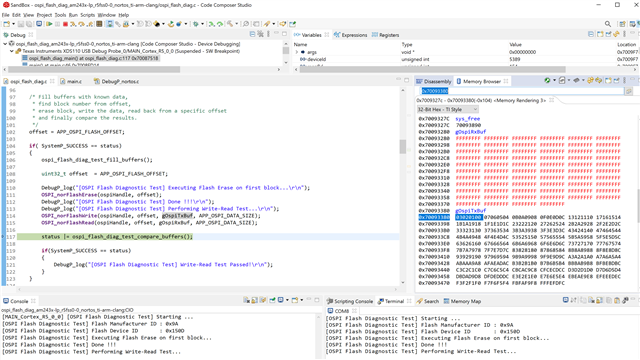

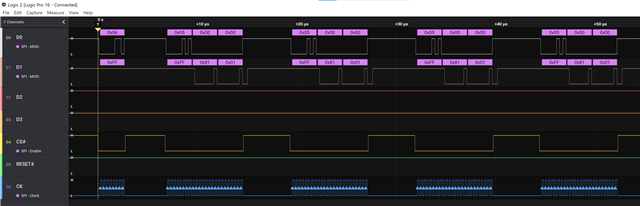

I have been working on the Beckhoff EtherCat slave stack. Specifically, I have been changing the contents of the slave EEPROM (which is emulated and stored in the OSPI Flash) using an EtherCAT master.

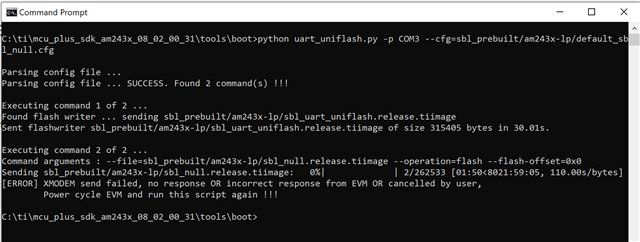

However, after doing this for a couple of times, the OSPI Flash no longer opens and the LP is 'bricked'. Even if I take the Hello World example and add Flash via Syscfg, the board initialisation fails. I am also unable to re-initialise the LP using the EVM setup process - it hangs on the second step (see image below).

The first time this happed (Sunday) I put it down to a faulty board. However, after a few more hours on a second LP that I borrowed, the same thing happened (TWO BRICKED LPs).

Is there any way to recover this?

Thanks,

Steve