Other Parts Discussed in Thread: SYSCONFIG

Hi Team,

In the context of this E2E thread below, I am creating another thread focused on loopback signals.

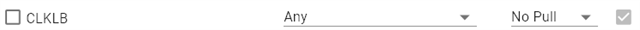

- Regarding GPMC_CLKLB and MMC1_CLKLB in SysConfig settings, if the customer were to not tick the box for these signals (as they do not have an associated ball), what would happen? I am assuming that they need to connect the pin, even though there is no ball associated, so is there any documentation that shows what this loopback signals are connected to and what it does? The documentation linked in the previous thread was OSPI/QSPI related, not GPMC/MMC1 related.

Best regards,

Mari Tsunoda