Part Number: SM470R1B1M-HT

Hi team,

Here's an issue from the customer may need your help:

For the same project, the compiler has two conflicting resolutions for the same bit-domain structure, as shown in the following code examples:

1) Bit domain structure definition:

typedef volatile struct

{

UBYTE rsv_ccr[3];

union

{

UBYTE ccr_UB;

struct

{

UBYTE CharLength_B3 : 3;//bit0~bit2

UBYTE Mode_B1 : 1;//bit3

UBYTE Async_B1 : 1;

UBYTE ParityEN_B1 : 1;

UBYTE Parity_B1 : 1;

UBYTE Stop_B1 : 1;//bit7

} ccr_ST;

} ccr_UN;

。。。

} SCI_ST;

Defines a pointer to type SCI_ST: SCI_ST * Sci_PST = &SCI1;

2) The main function has a C operating instruction

Sci_PST->ccr_UN.ccr_ST.CharLength_B3 = 7;

3) The initialization function has a C operating instruction

Sci_PST->ccr_UN.ccr_ST.CharLength_B3 = 7;

4) The result compiled within the main function and the initialization function is conflicting

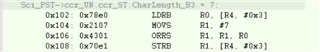

Within the main function:

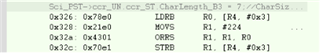

With the initialize function:

5) Conflicting: The main function assumes that the bit field member "CharLength_B3" is placed in the lower 3 bits. The initialization function assumes that the bit field member "CharLength_B3" is placed in the upper 3 bits.

Why is that?

Could you help check this case? Thanks.

Best Regards,

Cherry