Part Number: AM2434

Hi Champ,

I am asking for my customer. Sorry for that I don't know much about Arm-based MCU.

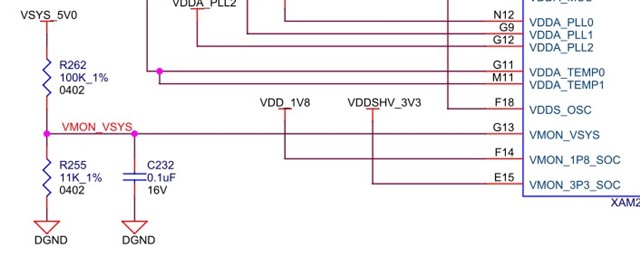

Customer's current design follows our EVM board with the pin VMON_VSYS in below screenshot.

I would like to ask the function and specification of this pin (VMON_VSYS) can be explained more clearly and easily. Though we have read the specification, still don't quite understand the purpose of this function. Would you elaborate more in details please ?

Also, the voltage level measured on VMON_VSYS is about 490mV from customer's design. Is it well-designed to meet the spec. ?

Thanks for any reply.

Best regard.