Hi all:

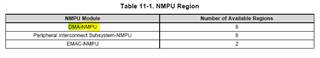

1. I find NMPU(new memory protection unit) in LC4357 datasheet (chapter 11 - system emory protection unit). Also when I read "Cortex-R5 Technical reference manual" , I find " chapter 7 - Memory protect unit" is very similar to NMPU.

Are they same? if not what difference?

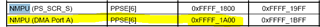

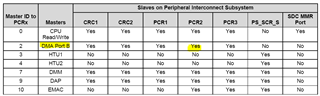

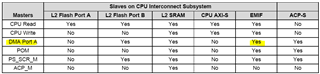

2. I also find there is a build-in MPU in DMA. According to the Figure 2-1 in the TRM, I am confused about built-in mpu, NMPU, and MPU. In my mind, when DMA accesss scr, it should have NMPU and MPU; when DMA access pcr, it only has one NMPU or build-in mpu?

3. In MPU, for the mpu Region Access Permission, I understand strongly odered, shareable, non shareable but what are the execution and no execution?

Best Wish

Li