Part Number: TM4C1294NCPDT

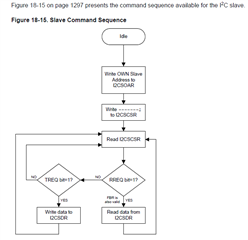

Hi, the TivaWare Peripheral Driver Library document (SW-TM4C-DRL-UG-2.1.3.156) states "the Tiva I2C modules support both sending and receiving data as either a master or a slave, and also support the simultaneous operation as both a master and a slave". Are there any examples for how to do this?

I've used the Tiva as an I2C master on numerous projects, but not a slave and looking at the documentation I'm not seeing what functions can be called to set it up as both a master and a slave at the same time.