王工您好:

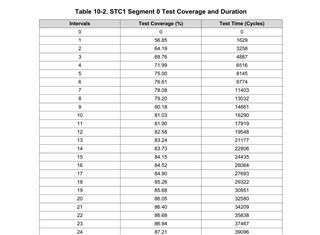

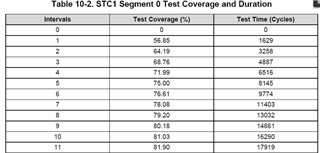

关于STC功能,我想咨询一下。如果intervalCount = 10,那么是每次之执行interval 10还是从1执行到10?restartInterval0 起到什么作用啊?

stcSelfTestConfig.stcClockDiv = 0; /* STC Clock divider = 1 */

stcSelfTestConfig.intervalCount = 10;

stcSelfTestConfig.restartInterval0 = TRUE; /* Start from interval 0 */

stcSelfTestConfig.timeoutCounter = 0xFFFFFFFF; /* Timeout counter*/

SL_SelfTest_STC(STC1_RUN, TRUE, &stcSelfTestConfig);