Hey,

Since a year we are using the DMA modul to trigger 2 ADC Channel. So far it worked very good.

Both channel are in ADC Group2 and they are triggered by a group conversion.

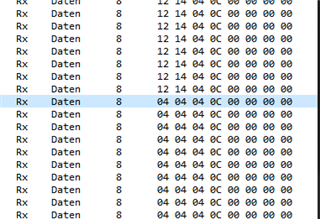

We added 2 more ADC Channel to the group conversion. After few hours the data are not correct for the first 2 ADC- Channel. We got an error caused by this data.

When we added a additional debug Variable, which was send out over CAN. unfortunately we can not reproduce the faulty behaviour with the debug variable.

Our ADC Channel:

| Description | ADC Channel | ADC Port | DMA CHANNEL | Buffer Size | Buffer Type |

| ADC_First1 | 18 | A | 3 | 100 | uint16 |

| ADC_First2 | 20 | A | 4 | 100 | uint16 |

| ADC_Additional1 | 4 | A | 1 | 30 | uint16 |

| ADC_Additional2 | 12 | A | 2 | 30 | uint16 |

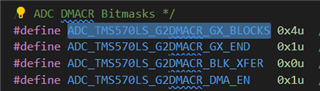

Configuration of the control Register: ADG2DMACR

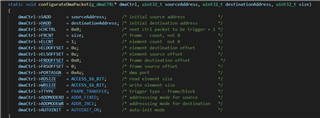

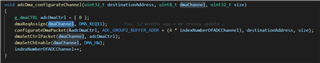

Here is our configuration and the function how the dma packet will be confugured.

________________________________________________

We have two questions:

1) what would be the effect of deactivation, while we validate the data and activate it afterwards again? Before we added the additional ADC Channel we deactivated the dma channel before we validated the data from the buffer.

dmaREG->HWCHENAS = (uint32)1U << channel;

2) What is the effect of ADC_TMS570LS_G2DMACR_GX_BLOCKS ?

We had a Software which where ADC_TMS570LS_G2DMACR_GX_BLOCKS was set to 2. In field tests it seams that this configuration was more stable, although we have 4 adc Channel which will be triggered by DMA.

Best Regards,

Thorben