Hello TI engineer:

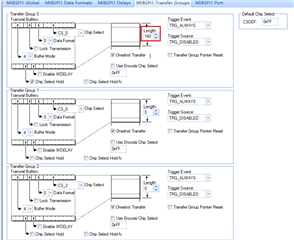

I want to enable 160 BUFFERS of mibSPI1 as following:

I had read the related QA in the forums:

All the suggest in the web link I have accepted and done

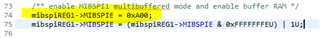

The extended buffer mode should be enabled before the buffers are initialized.

/** enable MIBSPI1 multibuffered mode and enable buffer RAM */

mibspiREG1->MIBSPIE = 0xA00;

mibspiREG1->MIBSPIE = (mibspiREG1->MIBSPIE & 0xFFFFFFFEU) | 1U;

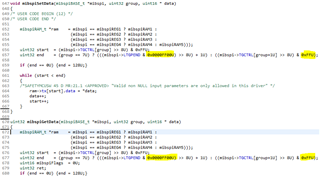

modify the code of mibspiSetData() and mibspiGetData() to set data for extended buffers and get data from the extended buffers. Change 7F to FF in the following two functions

uint32 end = (group == 7U) ? (((mibspi->LTGPEND & 0x0000FF00U) >> 8U) + 1U) : ((mibspi->TGCTRL[group+1U] >> 8U) & 0xFFU);

I was able to crossing data before enabling MıbSPI1 256 byte buffer between 2 MCUs. But after the change we made, MCU always reads as 0 via SPI. Maybe it can not receive any byte

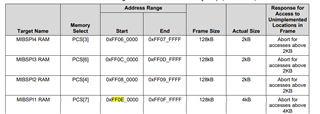

I found the doubt point in the HL_reg_mibspi.h, the SPI1 support 256 buffer, any problem?

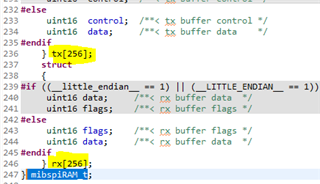

/** @struct mibspiRamBase

* @brief MIBSPI Buffer RAM Definition

*

* This structure is used to access the MIBSPI buffer memory.

*/

/** @typedef mibspiRAM_t

* @brief MIBSPI RAM Type Definition

*

* This type is used to access the MIBSPI RAM.

*/

typedef volatile struct mibspiRamBase

{

struct

{

#if ((__little_endian__ == 1) || (__LITTLE_ENDIAN__ == 1))

uint16 data; /**< tx buffer data */

uint16 control; /**< tx buffer control */

#else

uint16 control; /**< tx buffer control */

uint16 data; /**< tx buffer data */

#endif

} tx[128];

struct

{

#if ((__little_endian__ == 1) || (__LITTLE_ENDIAN__ == 1))

uint16 data; /**< rx buffer data */

uint16 flags; /**< rx buffer flags */

#else

uint16 flags; /**< rx buffer flags */

uint16 data; /**< rx buffer data */

#endif

} rx[128];

} mibspiRAM_t;

When I modified the "rx[128]" and "tx[128]" to "rx[256]" and "tx[256]" , it didn't worked