Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

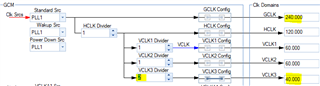

I am trying to get the 570LC4357 clock setup with 300MHz CPU clock (GCLK) and 40MHz EMIF clock (this cannot change due to onetime programmable FPGA having a 40MHz clock). What I can see from the HALCoGen tool is, the EMIF bus is tied to VCLK3 and VCLK is driven from the same PLL output as the GCLK, which doesn’t give me an option to generate 40MHz for VCLK3 with 300MHz for GCLK.

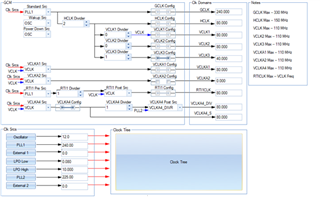

Are there any undocumented features to do this trick? Below is what I have in HALCoGen.