Hello,

is it correct that both Ethernet ports for CPSW and ICSSG are available at the same time (no pin limitations). However, the overlap of CPSW and ICSSG is limited to only 1 port?

Regards, Holger

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

is it correct that both Ethernet ports for CPSW and ICSSG are available at the same time (no pin limitations). However, the overlap of CPSW and ICSSG is limited to only 1 port?

Regards, Holger

Hello Holger,

Not sure if I understand your question. The pinmux for AM243x supports a max of up to 4x ethernet instances. The CPSW3G can support (2x RMII or 2x RGMII) and the PRU-ICSS can support (2x MII or 2x RMII or 2x RGMII). This can be instantiated using any combination of these modules as long as a valid pinmux solution exists. Please use the SysConfig-PinMux Tool to test your various use case options.

Best Regards,

Zackary Fleenor

Hello Zackary,

sorry for not clear. Customer wants to design one HW/PCB for different applications. One application he wants to use CPSW for standard Ethernet and for the other application he wants to use ICSS for fieldbus Ethernet. So the CPSW and ICSS should use the same pins for the Ethernet transceiver so that he can use same PCB and don't have to use external MUX. What I know is that one port has overlayed pins between CPSW and ICSS.

Regards, Holger

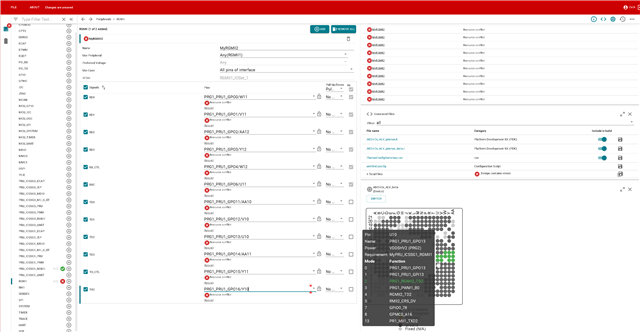

Thank you for the additional clarification. This type of usage can also be confirmed with the SysConfig-PinMux Tool. Please see the screenshot below showing clear overlap between CPSW-RGMII1 and ICCSG1-RGMII2. Using these pins would allow customer to create singular HW design as you've mentioned (other solutions will also exist).

| Ball | CPSW | ICSS |

| W11 | RD0 (RGMII1) | RGMII2_RD0 |

| V11 | RD1 (RGMII1) | RGMII2_RD1 |

| AA12 | RD2 (RGMII1) | RGMII2_RD2 |

| Y12 | RD3 (RGMII1) | RGMII2_RD3 |

|

W12 |

RX_CTL (RGMII1) | RGMII2_RX_CTL |

| U11 | RXC (RGMII1) | RGMII2_RXC |

|

AA10 |

TD0 (RGMII1) | RGMII2_TD0 |

| V10 | TD1 (RGMII1) | RGMII2_TD1 |

| U10 | TD2 (RGMII1) | RGMII2_TD2 |

| AA11 | TD3 (RGMII1) | RGMII2_TD3 |

| Y11 | TX_CTL (RGMII1) | RGMII2_TX_CTL |

| Y10 | TXC (RGMII1) | RGMII2_TXC |

Best Regards,

Zackary Fleenor