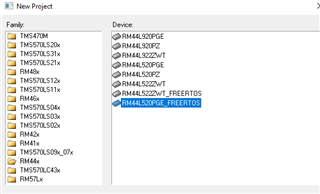

Part Number: RM44L520

Other Parts Discussed in Thread: HALCOGEN,

Hello,

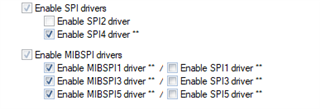

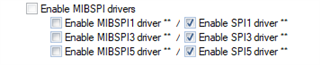

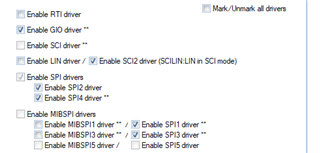

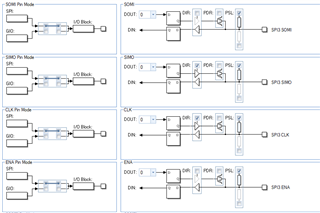

I am trying to configure SCI3 to communication with another internal device using pins 36,38,35, and 34. I have configured them all in halcogen under the SPI3 tab and have selected the SPI3 driver in the driver select menu. My confusion is coming from the fact that the documentation for this processor only lists registers labeled as MibSPI3 not just SPI3. Am I able to use just SPI on these pins or do I have to use MibSPI? I am porting over code to service a separate processor so If I can continue to use SPI that would be preferable.