Other Parts Discussed in Thread: HALCOGEN,

Hello Team,

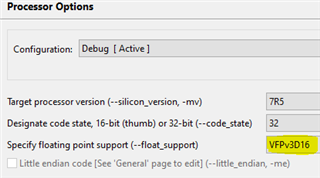

I am trying to enable FreeRTOS in our Software. For the Start, I have tried to run the " example_freeRTOSBlinky.c".

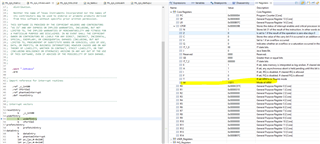

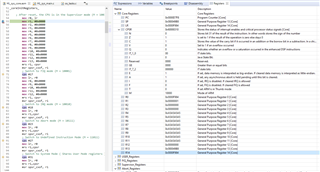

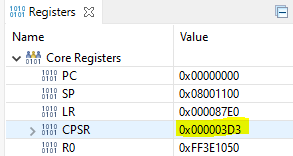

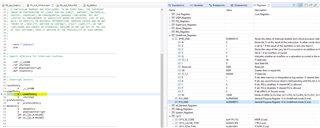

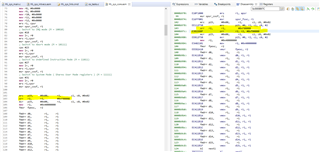

The SW works fine until I do a Reset on the CCS. The SW gets stuck in undefEntry. I could see that the address which causes this Issue is "0x0000B97C".

Can the team give me an Insight on why is this happening and how can this be resolved.

Thanks and Regards,

Sakti Kumar Padhy