Part Number: AM2634

Hi,

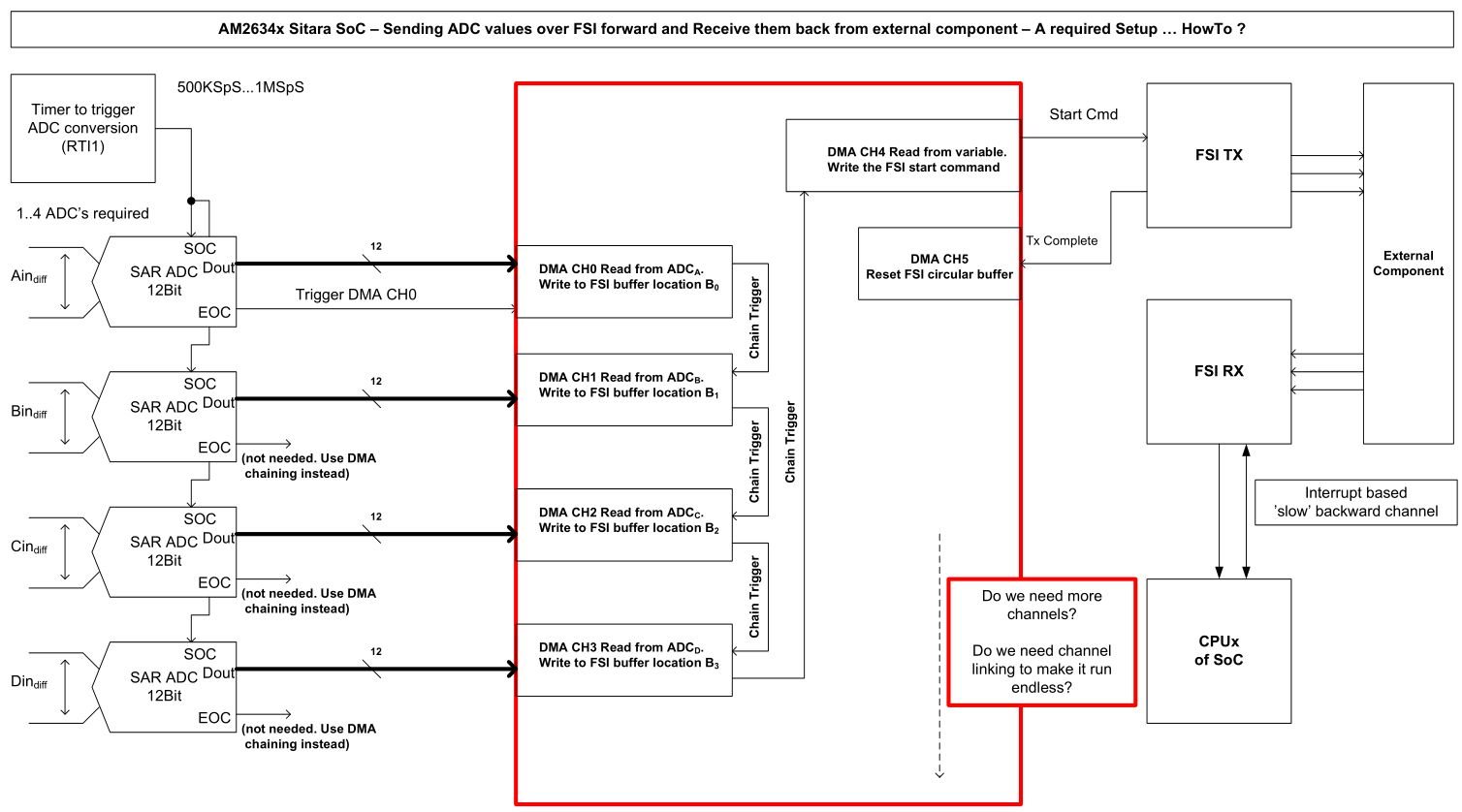

I need to transfer a couple (4) of sampled values from four ADC's over a fast serial link channel to a companion chip using the EDMA and the FSI from the AM2634. Once configured this data transfer of these sampled values has to run endless without any further CPU intervention. In this context the CPU code is used for configuration purpose only and for exception handling in case of troubles.

The setup / configuration is done the following way:

- The ADC's do sample the voltage on one differential input (named Ai, Bi, Ci and Di). The sampled value is stored in one of the result register for each ADC. The sampling interval shall be ~ 2usec.

- ADC_A (from input Ai) shall trigger the EDMA channel (CH0) through its end of conversion event (EOC). This channel shall transfer the sampled value SAMPLE_A into the data RAM section of the FSI channel. Once this single word transfer completes it shall 'trigger' (using 'chaining' ?) the next EDMA channel (CH1) to do the very same but this time for the sample 'SAMPLE_B' from ADC_B representing Bi. The destination address for this single word transfer is up by two bytes in order to align the sampled value of Bi just above SAMPLE_A of Ai. This mechanism repeats for Ci and Di using EDMA channels CH2 and CH3.

- EDMA channel CH3 'triggers' CH4 which basically writes the code/cmd-word into the appropriate FSI channel to start transferring the four sampled values to the external companion chip.

- Once the FSI transmission completes a fifth DMA channel (CH5) shall be used to reset the internal RAM address pointer within the Tx FSI channel used, in order to guarantee that the next four samples are being xferred correctly. The data RAM within the FSI channel is not a FIFO. Therefore an address pointer addressing up to 16 words needs to be reseted each time after the current transmission completes. Otherwise the position within the data RAM of the Tx FSI would be different.

(A block diagram is attached that show what I try to accomplish)

So far so good. Now the questions:

Q1: How do I need to setup the ParRAM of the EDMA to accomplish this? Especially how do I configure the option register within the ParRAM?

Q2: Do I need channel linking, since it has to run endless, once setup?

Q3: Is there an example that shall be used in order to accomplish this setup?

Q4: The TRM of the AM2634 is not complete in respect to the EMDA description. I did find another document from TI. "KeyStone Architecture

Enhanced Direct Memory Access (EDMA3) Controller User's Guide" (sprugs5b.pdf) Can this be used for the EDMA3 on the AM2634?

br

Markus