I'm running JTAG Boundary Scan tests using a JTAG Technologies test setup.

I’ve been able to create an individual interconnect test for my test board CPLD and everything worked.

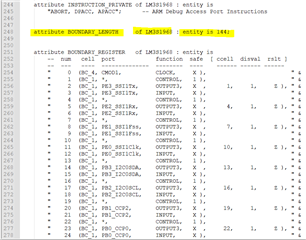

When I created one for the LM3S1968 108-ball BGA, the interconnect test failed. I was able to verify that the output pattern was driving the pins correctly, but the input pattern being read failed.

For instance, the 2 pins CMOD0 and CMOD1 are hard wired to ground, but the received JTAG pattern show them high.

The test patterns for PA0, PA2, PA3, PA4 and PA5 all show up correctly. All other patterns show up as low, except for CMOD0 and CMOD1 which show up as high.

Could the part be in the wrong mode? I have the RST(low) signal tied high.

Is there some way to tell when the part is sampling data correctly for the sequence? Would it show up in the BSDL or the test pattern?