Part Number: AM2432

Other Parts Discussed in Thread: ADS131M08,

Hello

I am working on interfacing an ads131m08 energy meter chip to a Sitara AM2432.

I have the SPI transaction being started on a falling-edge signal interrupt from the energy meter DRDY pin.

The interrupt triggers the 40 byte SPI transaction to clock out the data frame.

I have the adc configured at SCLK = 25MHz and CLKIN = 8.192MHz

I am getting intermittent CRC fails with this configuration, but these go away when I reduce SCLK to 14MHz. I am using ~15cm jumper cables to connect the am2432 GP EVM J1 safety connector to the ads131m08 evm. Is it likely that these CRC fails are due to the limitations of using jumper cables?

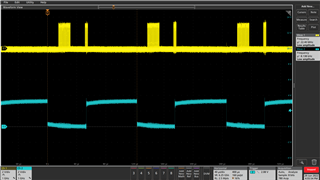

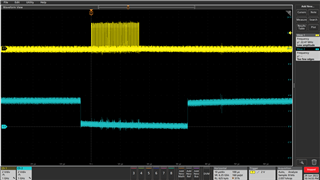

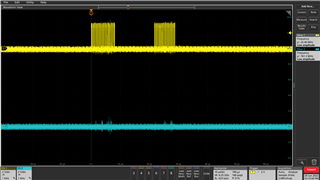

Additionally, in the photo below the yellow line is SCLK and the blue line is DRDY.

Why is there a ~20uS delay before starting the SPI transaction, and why is there a delay in the middle of the SPI transaction?