Other Parts Discussed in Thread: HALCOGEN

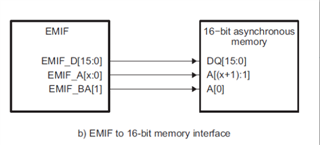

We are trying to integrate Cypress Asynchronous SRAM (CY7C1061G). The EMIF lines of the MCU is connected as described in the Technical Reference Manual of the MCU

The SRAM CE is connected to EMIF_nCS[2] (L17) line. But the EMIF module doesn't seem to drive the CS line at all.

We have ensured the correct mux in Halcogen. The Halcogen project files are attached. Following is the snippet of code we are trying to run

#define SRAM_ADDR1 (volatile UINT16 * )(0x60000000)

typedef unsigned short UINT16;

int main(void)

{

bool bPass = true;

volatile UINT16 uReadBack1,uReadBack2,uReadBack3,uReadBack4,uReadBack5,uReadBack6;

volatile UINT16 *uAddr = SRAM_ADDR1;

volatile UINT16 uData[8];

uReadBack1=0xFFFF;

uReadBack2=0xFFFF;

uReadBack3=0xFFFF;

uReadBack4=0xFFFF;

_cacheDisable_();

//GioSetup();

//gioSetBit(gioPORTB,4,1);

emif_ASYNC1Init();

wait(10000000);

//gioSetBit(gioPORTB,4,0);

//*uAddr = 0x1111;

for (int i=0; i<1000;i++)

{

*SRAM_ADDR1=0xAAAA;

}

uReadBack1 = *uAddr;