Hi everybody.

We met a I2C problem during immunity test with undesired leakage (~100MHz) which coupled to the bus.

The main issue looks like corruption of one or more clocks in a message (depends at leakage).

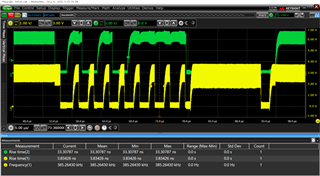

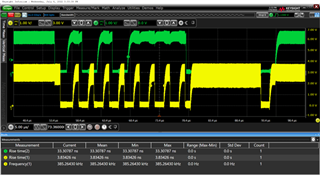

The next oscillogram show reading message and holding line by slave. It happens due to missing one clock and slave is waiting another one to set ACK.

So, this can be fixed using workaround by adding additional clocks to release SDA to normal state.

Generally it depends which clock was corrupted, sometimes the slave can detect his address.

Clock corrupting happens on the MCU side (not a slave), it was verified with MCU standalone.

Used MCU pins: PA6/PA7, HW I2C.

Rise time: ~220nS, Frequency ~400kHz.

So, we fastly implemented SW I2C by toogling GPIOs configured as Open-Drain and it works fine even with huge leakage comparing with previous one.

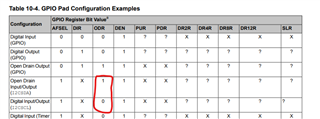

Quick looking of MCU spec and some difference between SDA and SCL was found:

![]()

Using debugger, GPIO registers were verified and SCL line is not in the Open Drain State.

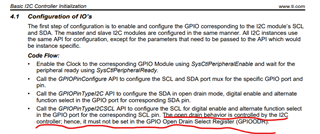

So, in the SPMA073 - application report has a more description why we should not do that.

----------------------------------------------------------------------------------------

Do you have any idea why clock can be corrupted like that?

Could you clarify which electrical difference between described cases (SCL OD behavior by I2C controller / SCL like open drain GPIO), if it exists?

Thanks!