Part Number: TMS570LS1224

Hi,

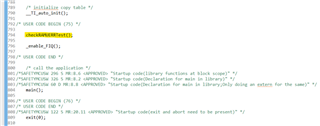

I am facing a scenario where enabling FIQ causes a prefetch abort only during a power on reset.

I am disconnecting the target after flashing the software and then i am doing a power on reset, the system didnt run as expected to debug the issue i connected back to the target and found that the system is stuck in prefetch handler.

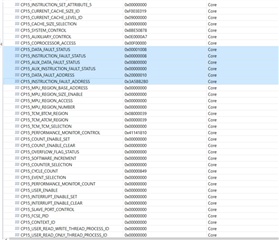

Instruction fault status register = 0x00000008

Instruction fault Address register = 0x3E5BB2B0

The SPSR_ABT indicates that the system was in FIQ mode. Only ESM interrupts are FIQ and all other interrupts are configured as IRQ

The system is running as expected in debug mode but not after a power on reset and I am not facing this problem if FIQ isnt enabled

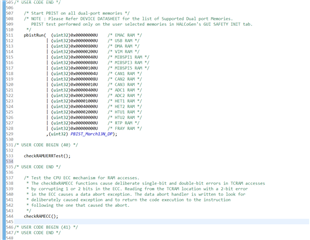

As a work around to this problem I am doing a S/W reset in prefetch abort handler and after the S/W reset the system runs as expected, but I really dont understand the root cause behind this. It would be really great if i could some help in resolving this issue.

Thanks.