Other Parts Discussed in Thread: EK-TM4C1294XL

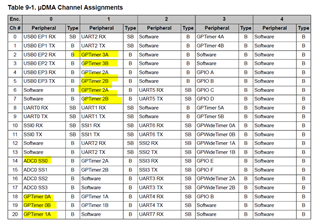

I use 4 Timers as PWM Mode.

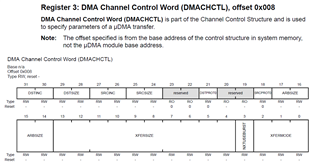

Every Timer has his own DMA Interrupt Signal to transfer 1 Item from Memory to his own Match Register to Change the DutyCycle.

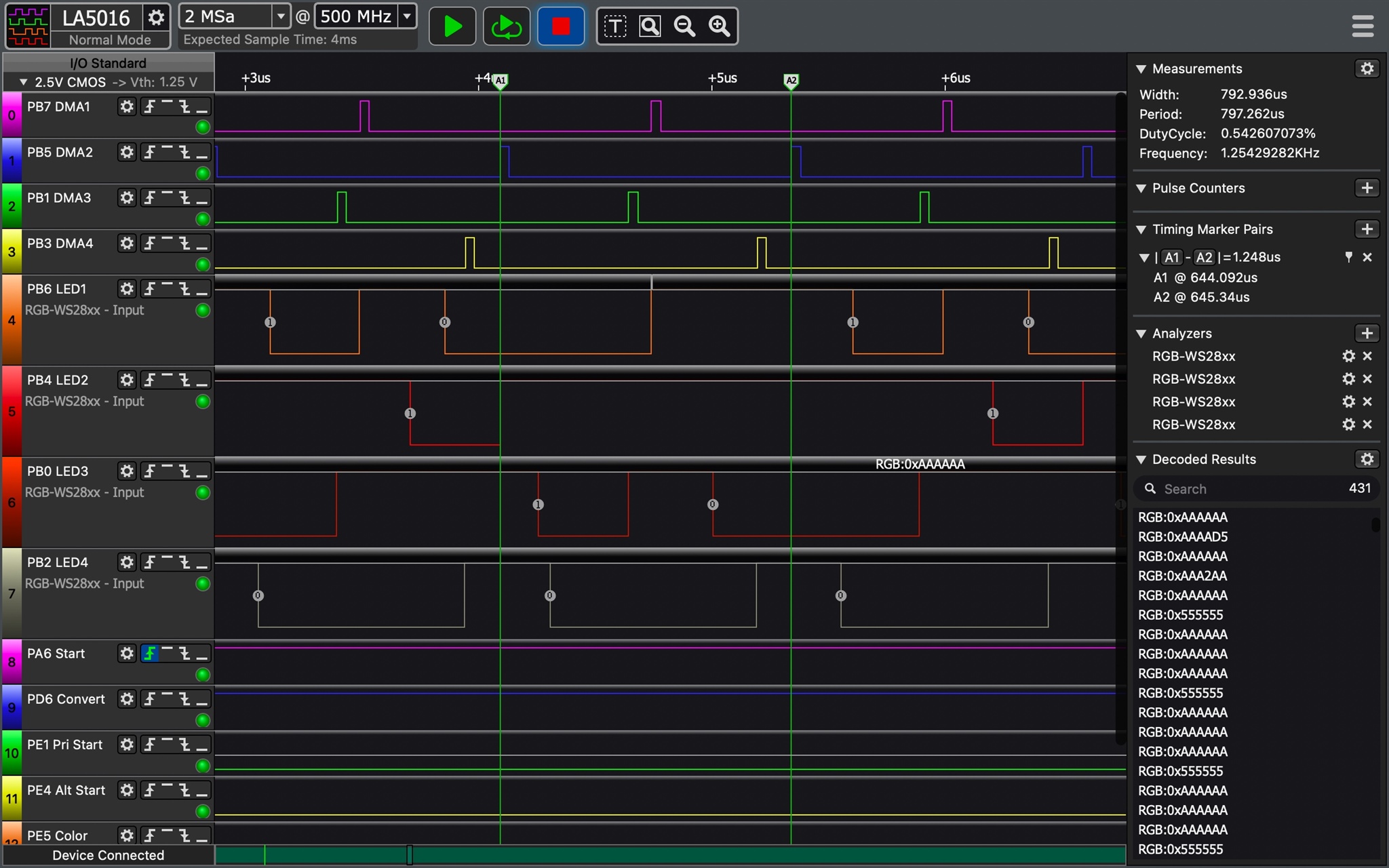

This is running good. But when I am activate uDMA for ADC Sampling to memory. My Timers PWM Signal sometimes is not running for one PWM Period.

Why? I test it so much to find the error. Iam out of ideas.

Here is a Picture. The failure is on channel 5 PB4 LED2. The Periode is complete high. When the uDMA signal comes to late, in the match register is an older value.

It is helpfuly to poste the code? That has more than 3000 lines code.