Hi experts,

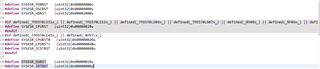

we noticed that a CPU-Reset triggered by the SW sets the reserved bit0 in SYSESR register:

The bit can only be reset by a Power On-Reset (nPORRST).

When checking the SYS_ESR for the cause of last reset this leads to SW signalling a failure since this bit is supposed to be 0.

(Q1) Is this a known bug?

(Q2) Should we always ignore bit 0 when checking for the cause of last reset?

Thank you and best regards,

Max