Other Parts Discussed in Thread: HALCOGEN

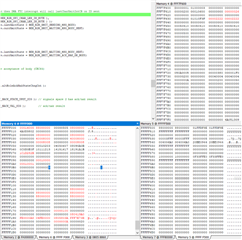

L2SRAM is MPU mapped in user mode. DMA already working OK from L2SRAM to SCI4.TX

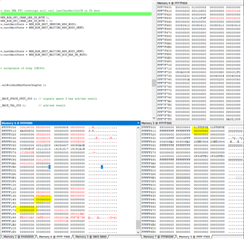

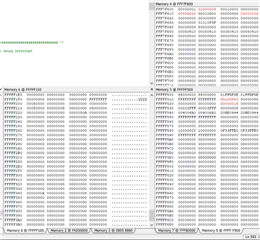

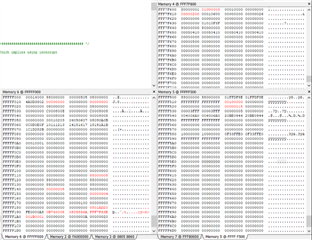

On a 16 bit transfer, I get DMA Bus Error (at ESM) on very first transfer from address 0x08058868 (L2SRAM) to 0xFFF7F63E (SPI2.TXDATA)

The application uses the SPI in legacy mode (so DMA channel 3). Only enabling SPI2CLK and SPI2SIMO pins as functional ones.

Manual sending of a single word (done before in the code, works fine and confirmed on scope.) First DMA access, that fails, creates no output at SPI SIMO.

The SDC only reports 0 on all of its registers. So I have no clue on cause of DMA Bus Error.